Our technology is built ground-up with a software-defined, data-driven system development approach.

AI’s growth has surged compute demand, with generative AI search costing nearly ten times more than standard search. Increased latency in searches or recommendation algorithms risks billions in losses, driving demand for efficient, specialized compute with new challenges.

Growing Complexity

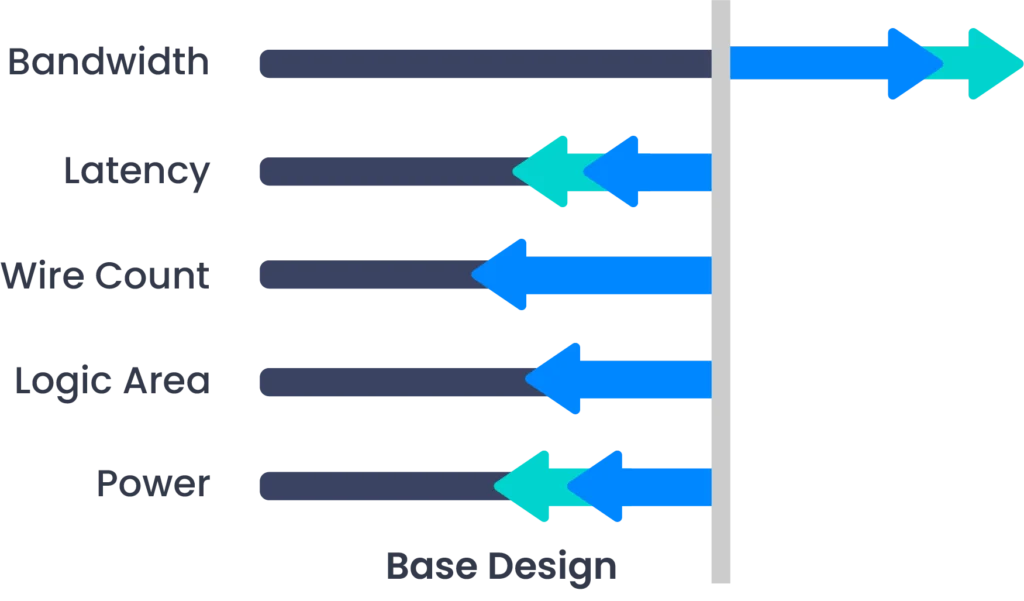

To support growing compute demands and energy costs, computing is shifting to specialized solutions with chiplet integration for optimal systems. This increases complexity and risk.

Performance and KPI Guarantees

Specialized computing platforms demand faster and more complex data interconnects, making it tougher to hit performance and latency KPIs, especially in multi-chip designs.

Costs are Becoming Prohibitive

Larger, complex designs increase energy for processing and data movement, expanding silicon footprint and power, raising silicon and packaging costs.

Time to Market Window is Shrinking

The breakneck pace of AI innovation demands designers nail critical KPIs on the first silicon.

Complexity

Performance and KPI Guarantees

Costs

Time to Market

Intelligent software-driven, customizable, system IP solutions for efficient, yet unprecedented scale for SoCs and chiplets.

Removes guesswork, reduces risk and cost of delivering complex high-performance systems.

Hyper-efficient transport fabric that can deliver 4 TB/s throughput in a single cluster, and scale to multiple PB/s for multi-chiplet AI applications, and support advanced high-bandwidth memories.

![]()

![]()

Extensive analysis and optimization through software platform enables a fabric that delivers guaranteed performance on target workloads and can be algorithmically optimized for future workloads.

![]()

![]()

![]()

![]()

![]()

Smart, customizable system IP solutions that drive unmatched efficiency and scale for SoCs and chiplets. Eliminate guesswork, slash risks, and cut costs while delivering high-performance systems.

The Baya Systems unified fabric provides a common transport supporting multiple protocols and coherency needs within a unified design flow. Physically-aware solutions can be optimized for power and area while delivering unprecedented performance, low latency and other key performance indicators (KPIs) from concept to deployment.

Common transport optimizes performance and area

Extensive flexibility in topologies and scale

Correct by construction and deadlock-free

Workload-based, static global and local optimization

Current Market Challenges

Baya Systems Benefits

Fabric channels in high performance silicon can take up to 20% of die area and power consumption

Up to 2x smaller fabric

vs standard mesh iso-performance

Performance bottlenecks created by protocol bridges, fabric transit points and longer routes

Up to 3 GHz and 32 PB/s

bisection bandwidth

Need for numerous protocol crossing bridges and scenic routes for communication flows

Lower latency

system and workload dependent

Deadlocks, QoS and tradeoffs unclear during design development

Up to 8 virtual channels

per network, deadlock-free, QoS built-in

Limited number of topologies, performance not scalable

8b-2048b channel width

with wide variety of topologies

Performance issues slow down architecture, complexity challenges slow down implementation

Data-driven design

and physically-aware implementation