Expanding Connections.

Accelerating Innovation.

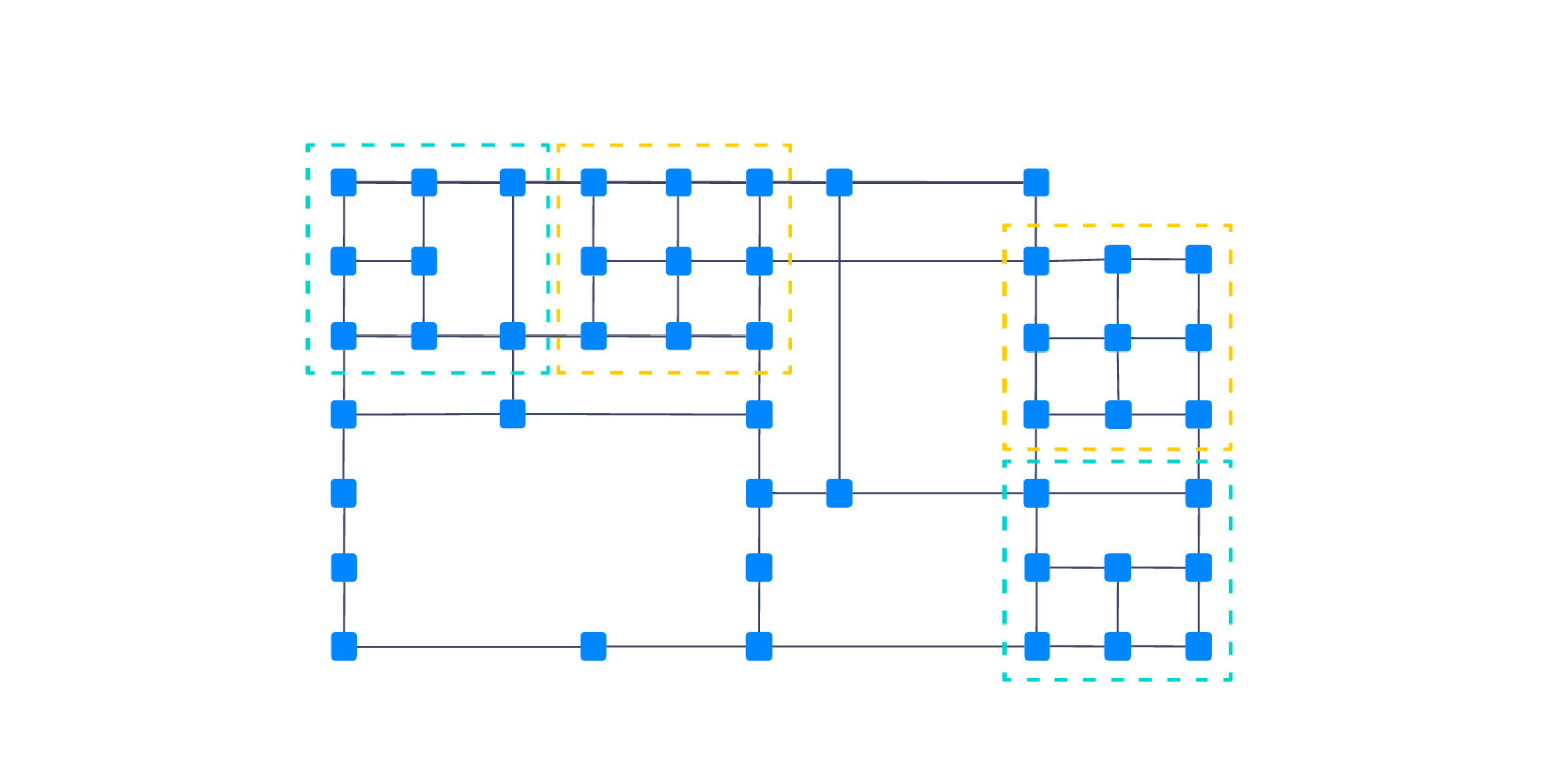

Baya Systems’ data-driven, software-defined, unified fabric boosts performance

and scalability for SoCs and chiplets.

Intelligent software-driven, customizable, system IP solutions for efficient, yet unprecedented scale for SoCs and chiplets.

Removes guesswork, reduces risk and cost of delivering complex high-performance systems.

![]()

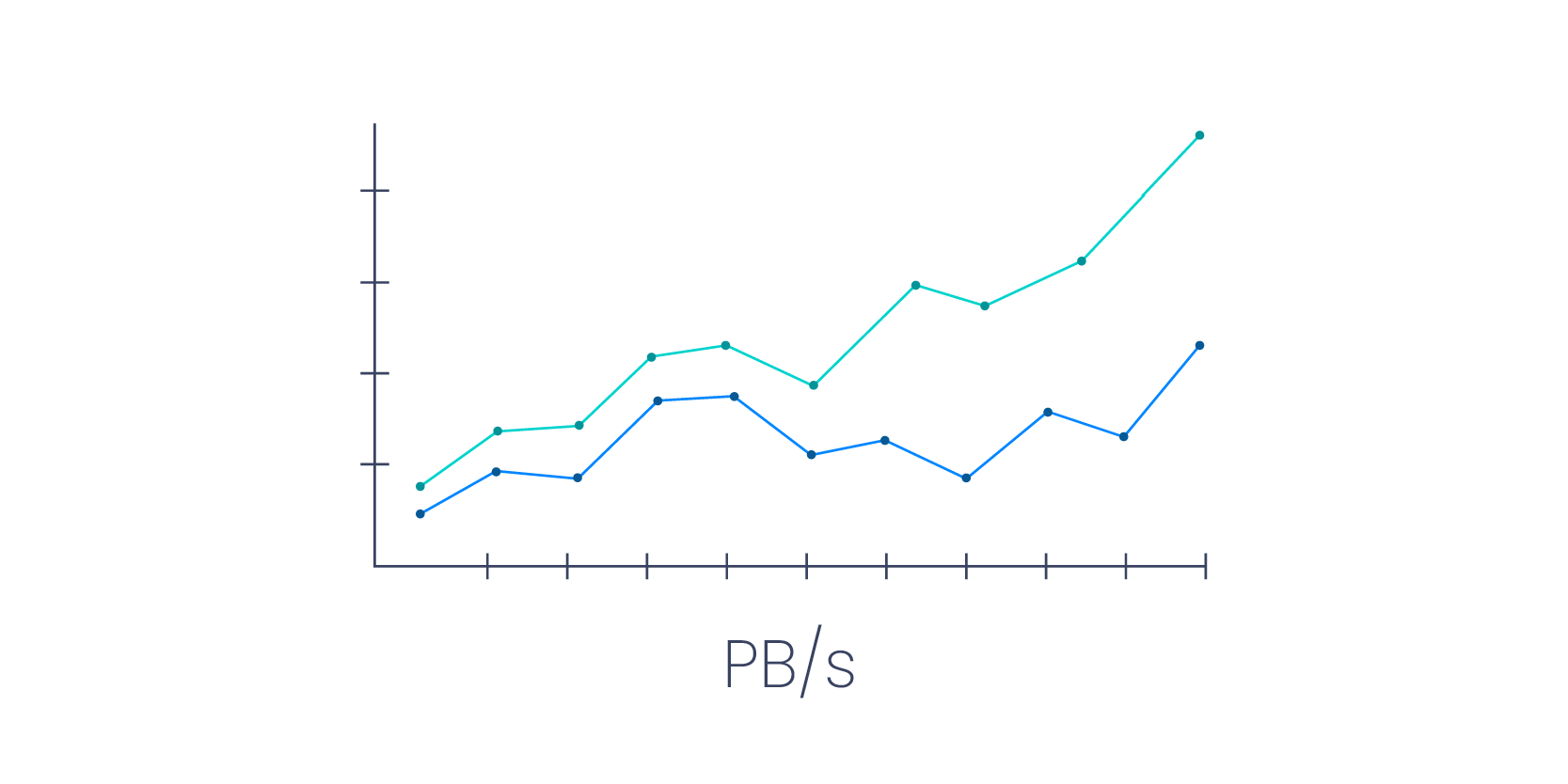

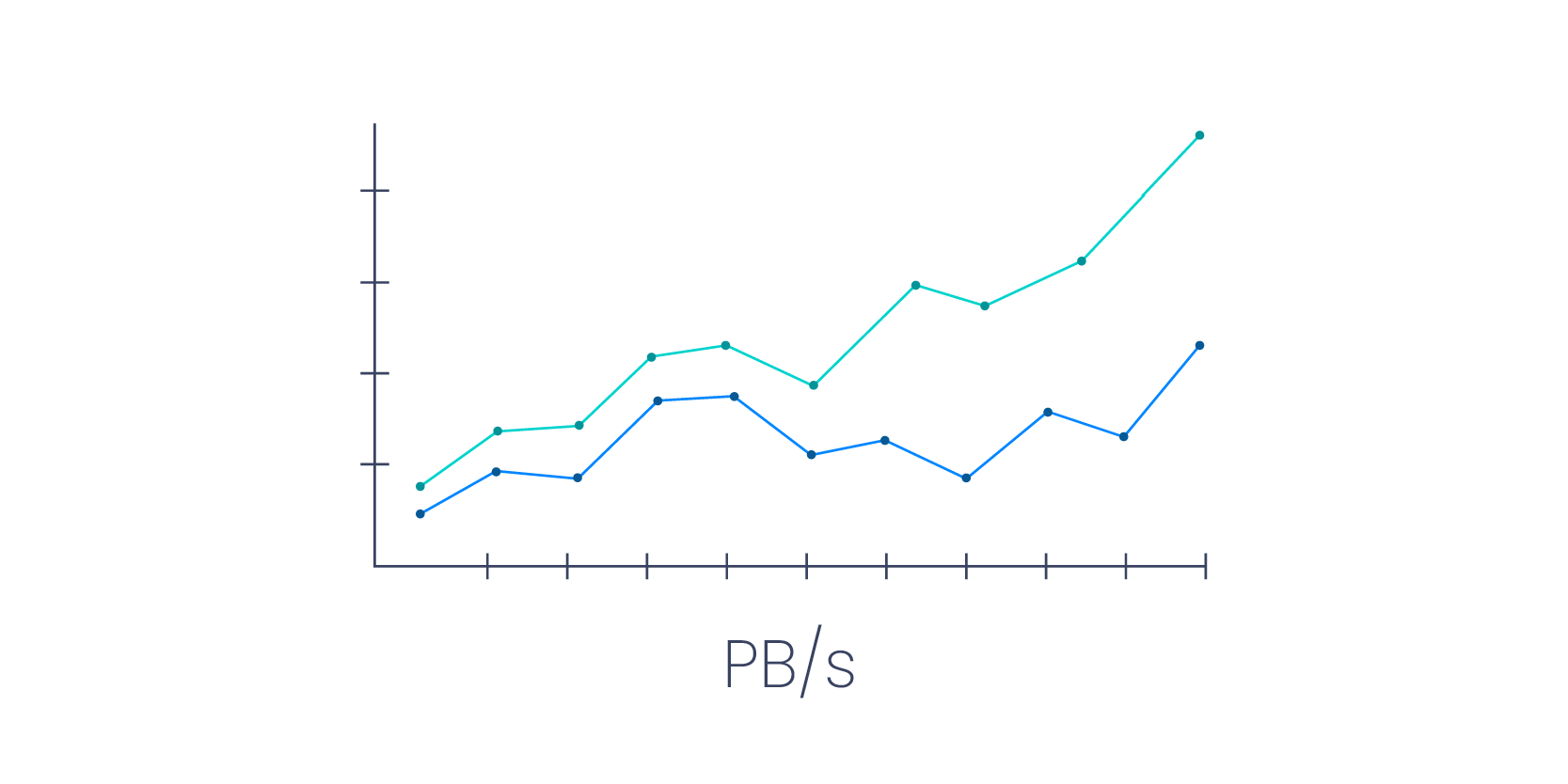

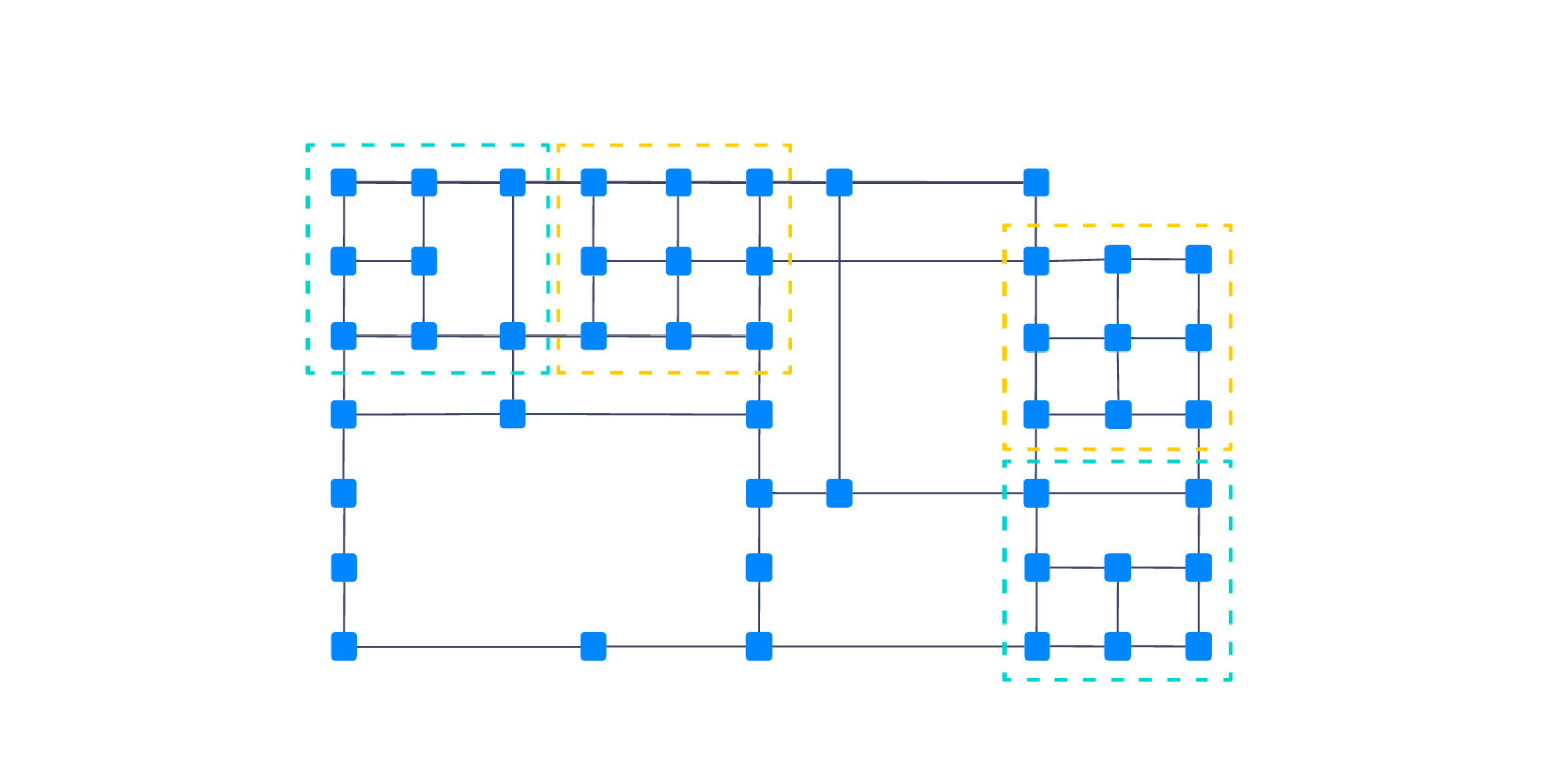

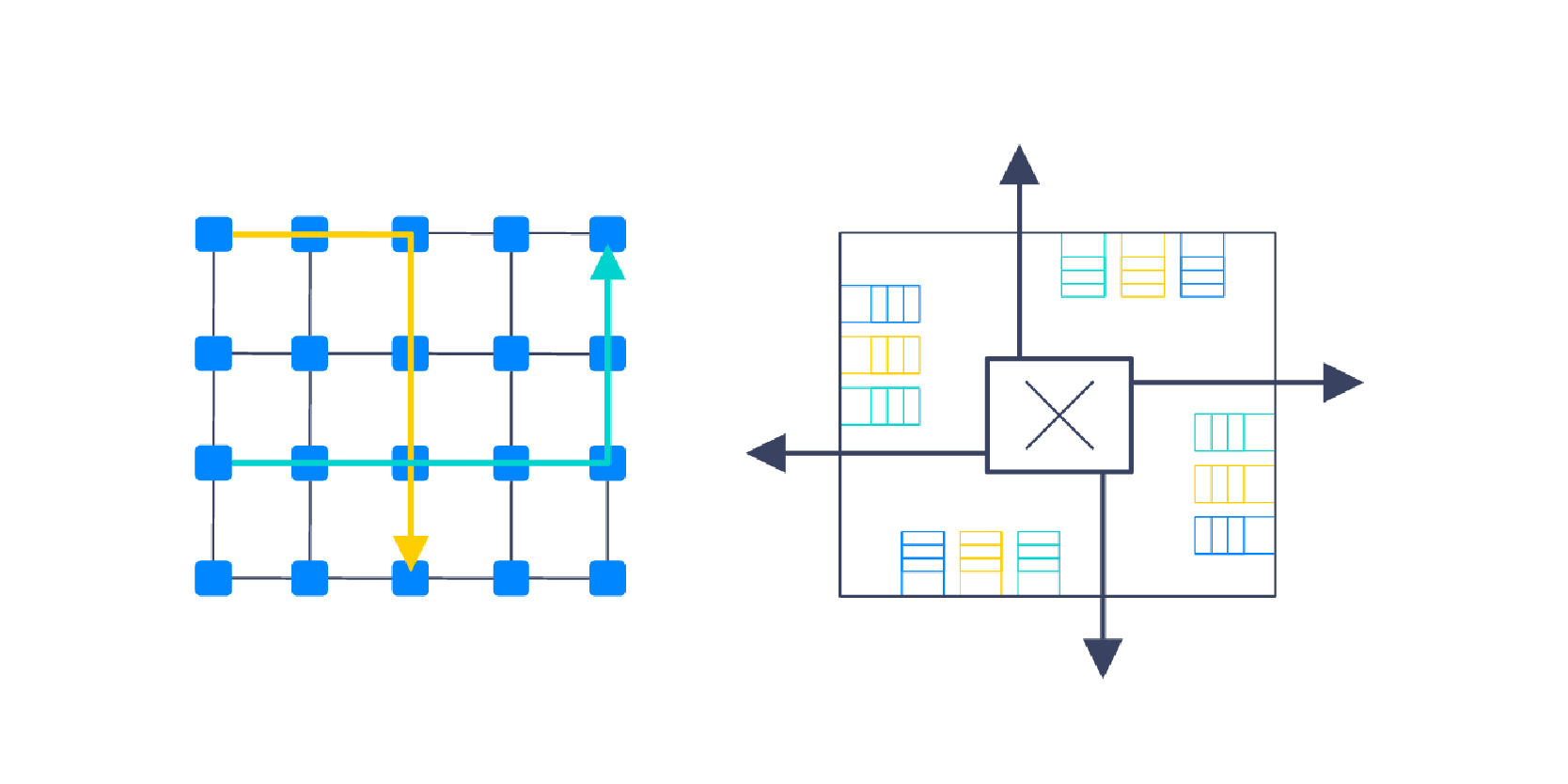

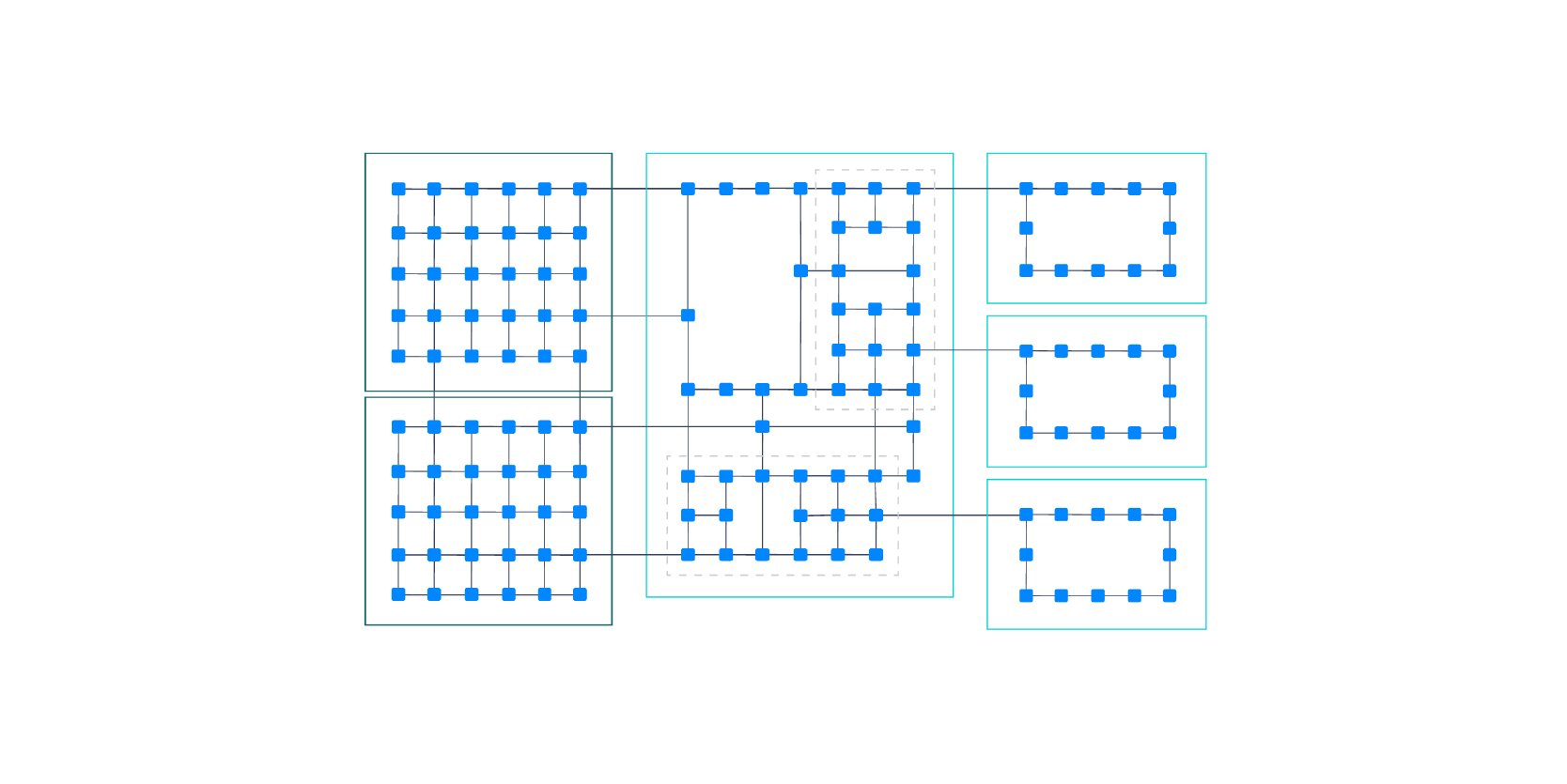

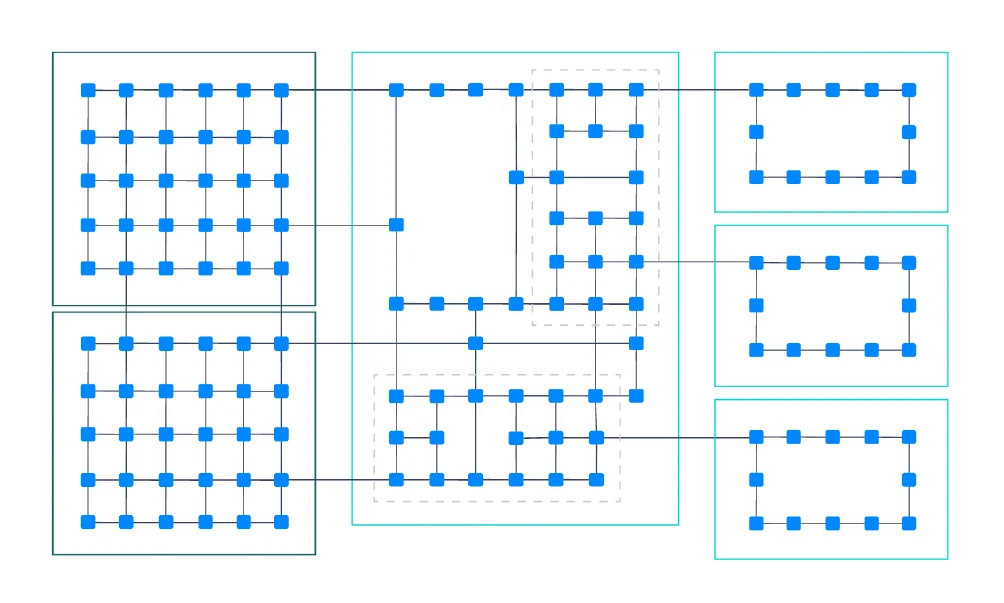

Hyper-efficient transport fabric that can deliver 4 TB/s throughput in a single cluster, and scale to multiple PB/s for multi-chiplet AI applications, and support advanced high-bandwidth memories.

![]()

![]()

![]()

![]()

![]()

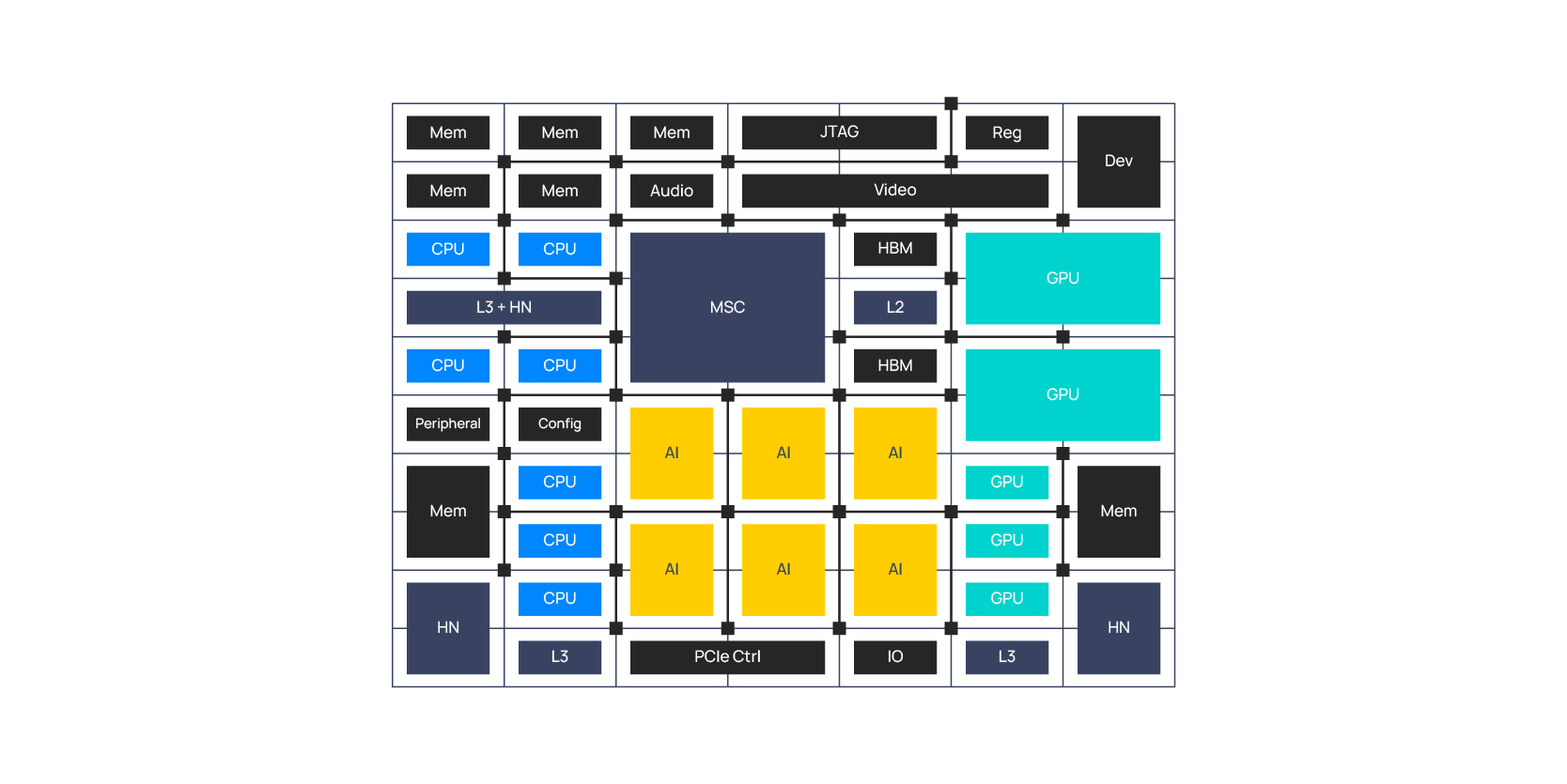

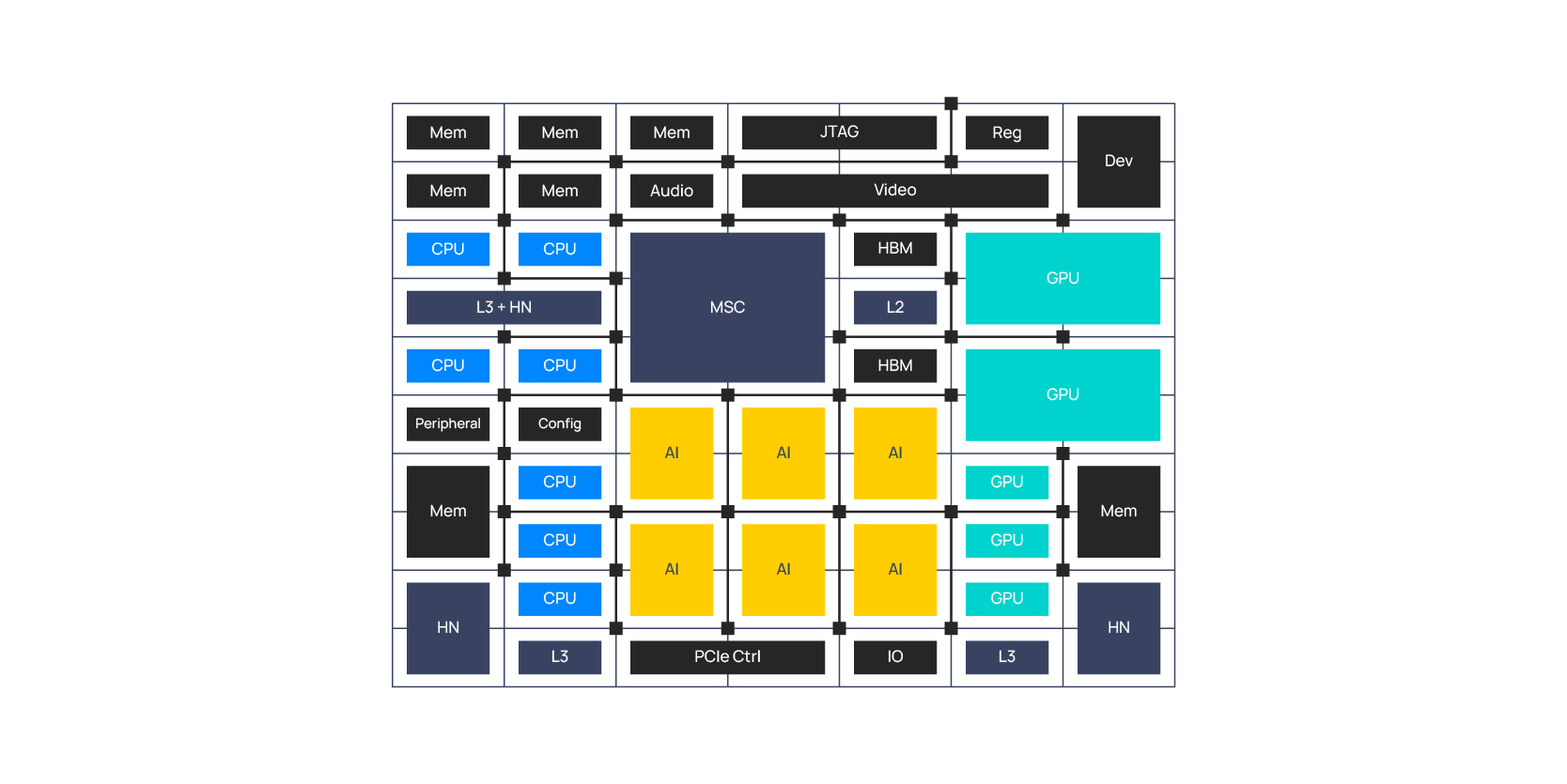

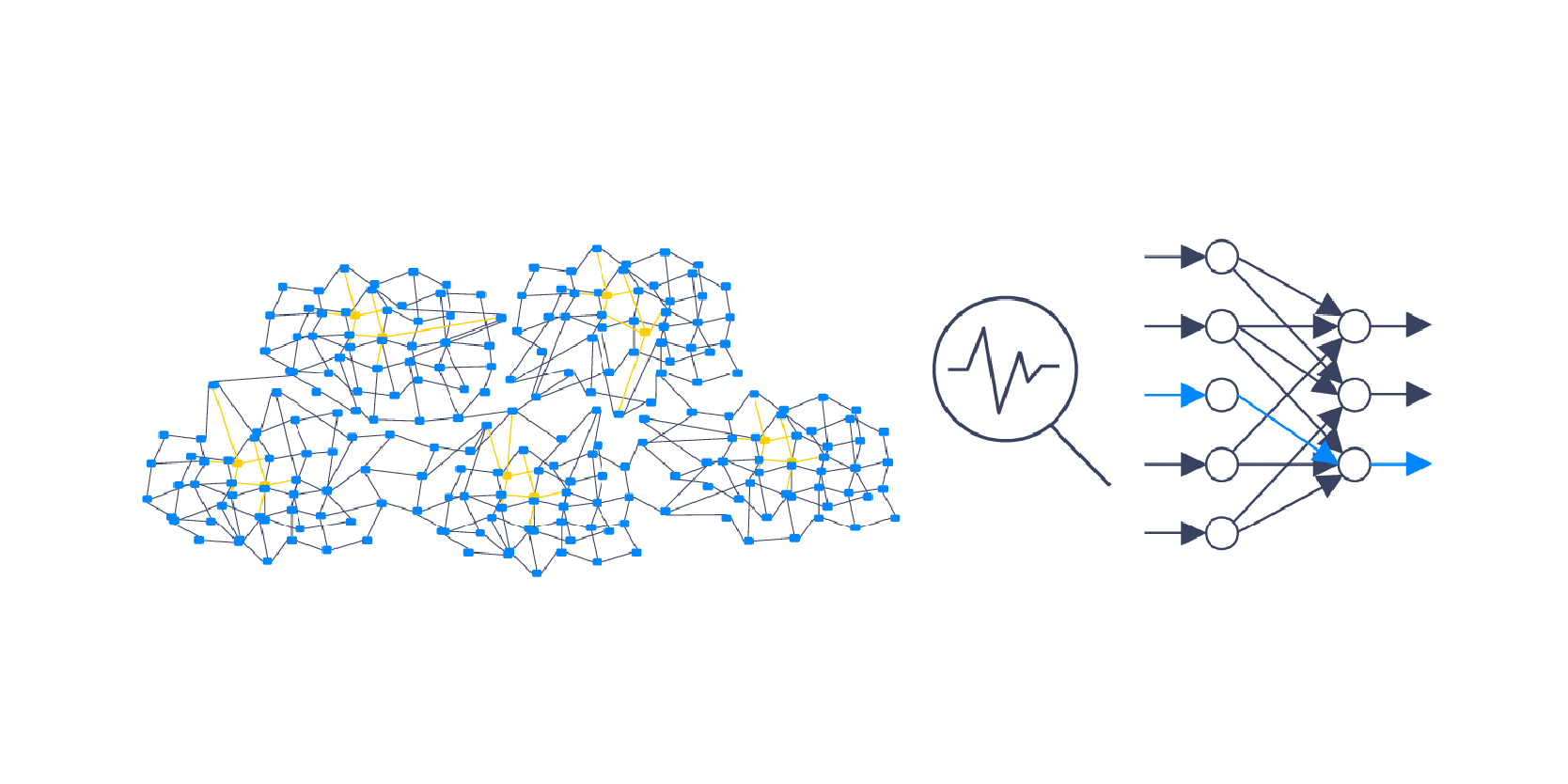

Extensive analysis and optimization through software platform enables a fabric that delivers guaranteed performance on target workloads and can be algorithmically optimized for future workloads.

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Built-in accurate, high speed simulator

Architecture and micro-architecture analysis and guidance

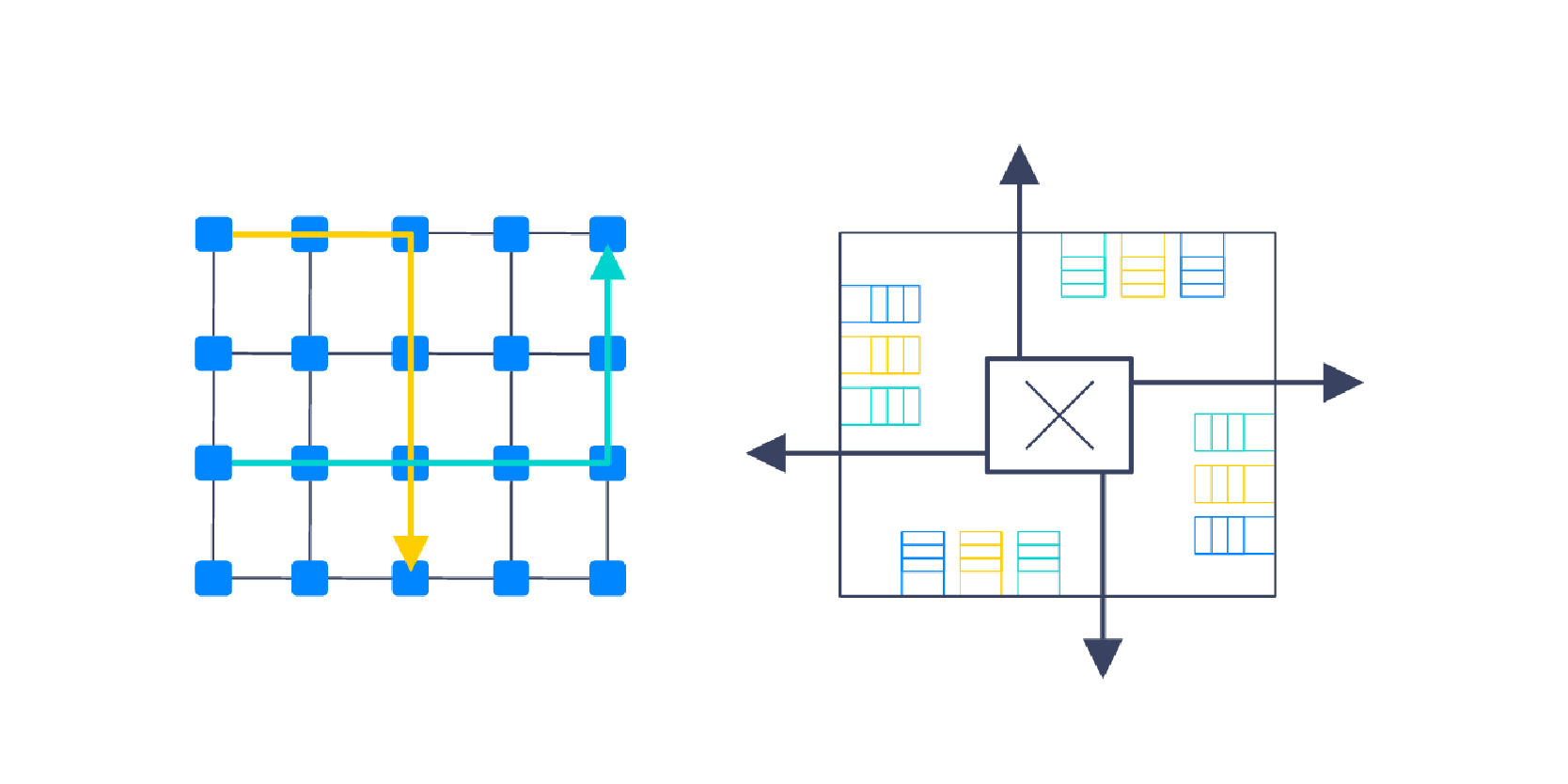

Algorithmic optimization and QoS

Correct by construction RTL generation

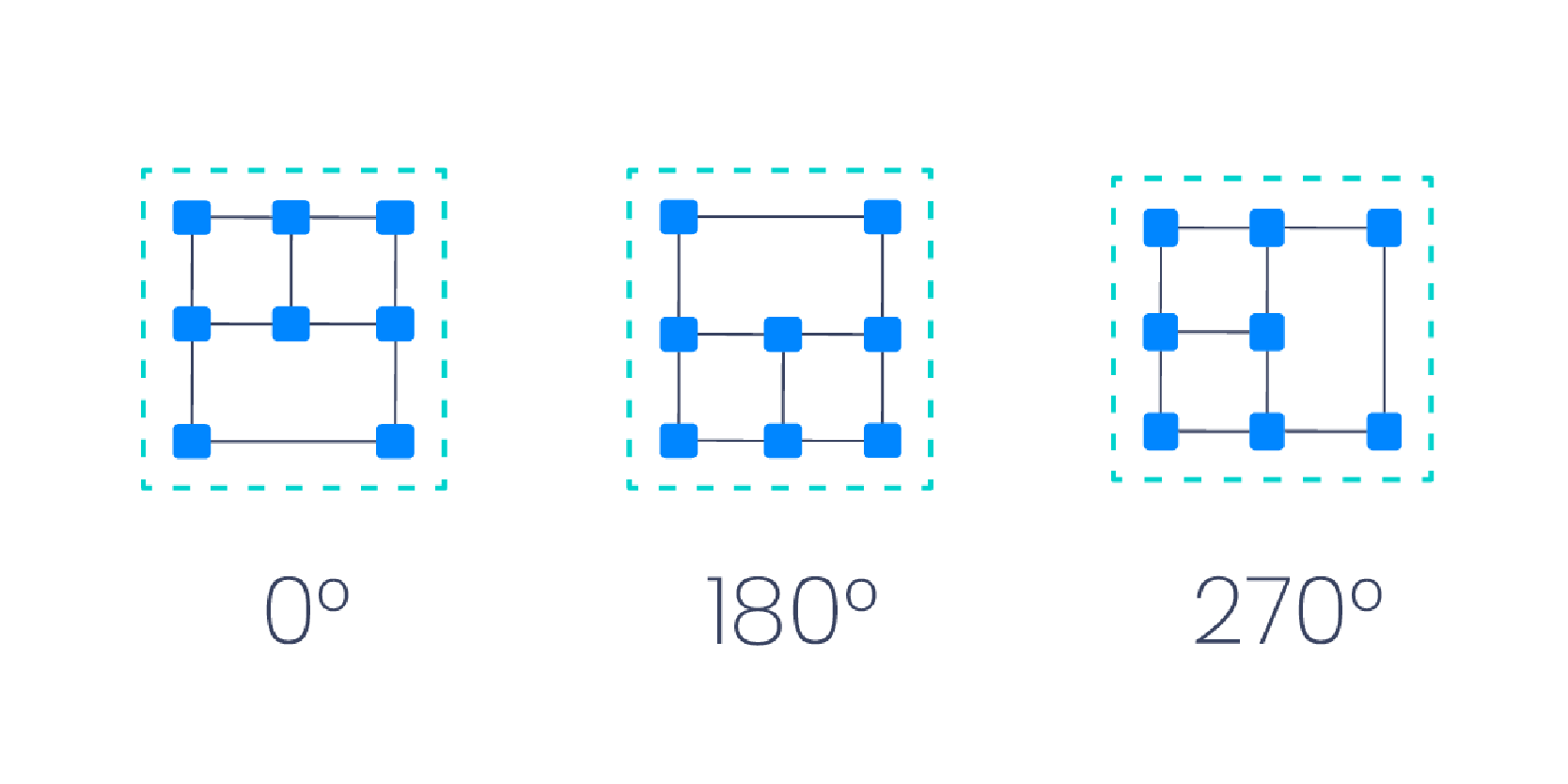

Tiling and physically aware implementation planning

High speed coherent and non-coherent AMBA 5 design

Customizable protocol fabric for AI and more

Multicast capability for advanced AI acceleration

Reliability, Availability, Serviceability and runtime QoS

We are actively hiring to build an exceptional team of engineers, architects and executives.