In modern AI systems, performance is increasingly determined not only by how fast processors compute—but by how efficiently data moves through the system.

Across the semiconductor industry, this shift is driving renewed focus on system architecture and interconnect design. As workloads scale and heterogeneous compute becomes the norm, architects must evaluate how CPUs, accelerators, memory subsystems, and chiplets interact long before RTL development begins. Understanding system-level data movement early has become essential to delivering predictable performance and hitting product timelines.

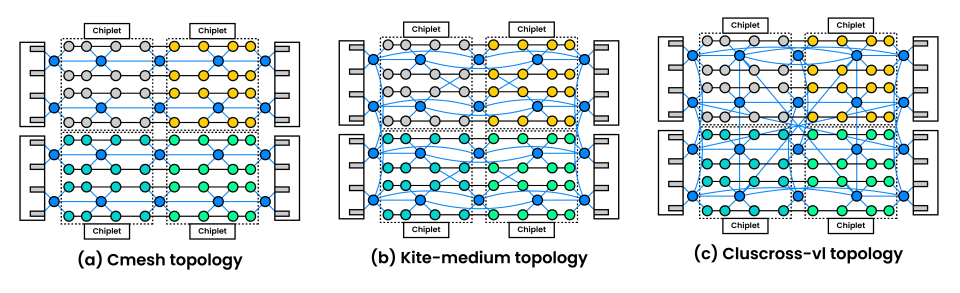

As AI, HPC, and heterogeneous SoC designs grow in complexity, data movement architecture has become as critical as compute. Modern systems rely on a diverse mix of CPUs, accelerators, memory subsystems, and chiplets that generate complex traffic patterns across the system interconnect. Understanding how these components interact—and how traffic flows through the system—has become a key part of early architecture exploration.

Yet accurately modeling these systems early in the design cycle remains difficult.

Traditional approaches often force architects to choose between accuracy and productivity. Full-system RTL simulation offers high fidelity but is expensive in engineering effort, simulation time, and compute resources. At the other extreme, architects often rely on simplified models or hand-coded protocol transactors. While faster, these approaches can miss important real-world behaviors and still require significant engineering effort to build and maintain.

What many systems teams need is a more effective modeling approach: one that runs fast enough for architecture exploration while accurately capturing the high-level behavior of the interconnect, providing clear guidance for making architectural decisions. Baya Systems and Synopsys are collaborating on the integration of Baya’s rapid NoC simulation capabilities with Synopsys Platform Architect product family. Synopsys Platform Architect for Multi-Die is a SystemC™ standards based power and performance analysis tool for architecture exploration helping optimize hardware-software partitioning, memory configuration, interconnect and IP selection-configuration. Baya’s FabricStudio platform enables architects early on to define and automatically generate NoC models that are accurate to the microarchitecture of systems. The integration between these two tools unlocks a powerful capability to evaluate realistic NOC behavior earlier in the system exploration stage.

System architects evaluating new designs typically face two imperfect choices.

Full RTL simulation can provide accurate system behavior but comes with significant tradeoffs:

Alternatively, teams sometimes construct system models using hand-coded AXI or CHI TLM transactors. While faster, these models often fail to capture realistic IP behavior and key network dynamics such as congestion, buffering, or backpressure.

As a result, answering fundamental architecture questions early becomes difficult:

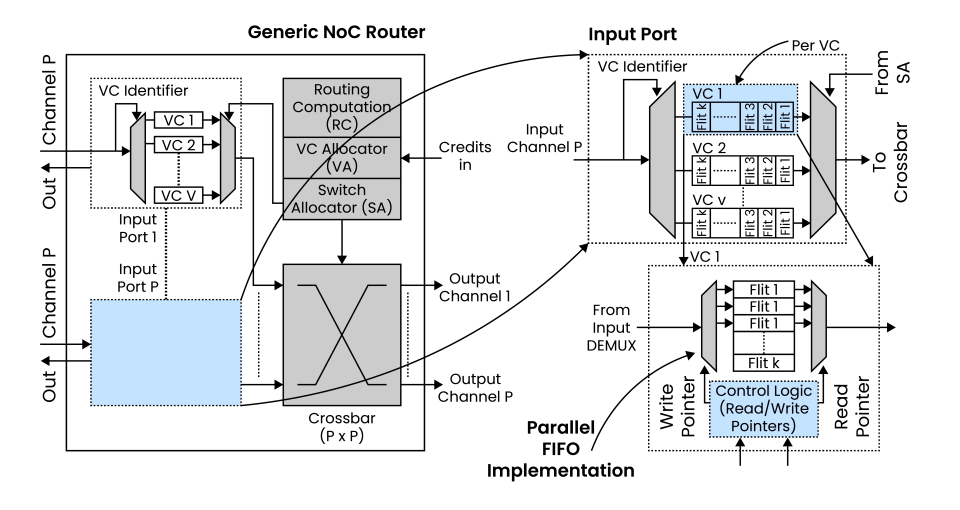

Baya’s approach introduces cycle-level NoC simulation directly into the system modeling workflow.

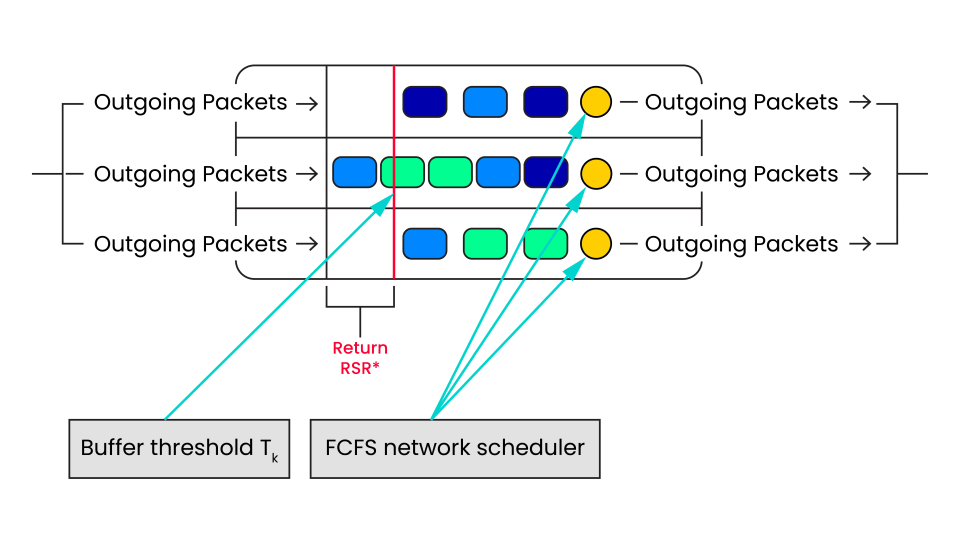

At the core of this capability is Baya’s flit-level NoC simulation engine, which models how packets move through routers, links, and buffers across the network. This allows the model to capture important network behaviors such as:

In the integrated workflow, FabricStudio acts as the entry point for defining the NoC architecture, while Platform Architect provides the broader system simulation environment.

Architects describe the NoC topology using FabricStudio’s Python-based architecture flow. From this configuration, FabricStudio automatically generates the SystemC-based NoC model.

The generated SystemC model can then be imported into Synopsys Platform Architect for Multi-Die, where it interacts with other system models such as CPUs, generic or IP-specific and highly accurate memory subsystems (like HBM, LPDDR, DDR), Die-2-Die or Chip-2-Chip IP (like UCIe, CXL, PCIe), and accelerators. Architects can simulate workloads and analyze how traffic flows through the network.

Because the simulator models flit-level behavior, architects can study real NoC characteristics such as bandwidth utilization, latency, and congestion under realistic traffic patterns.

Reducing integration overhead is critical for system architects.

The Baya NoC simulator’s external-facing API supports both C++-based and standard SystemC-based, and ARM AMBA TLM 2.0 Library interface, supporting both AXI and CHI protocols. Synopsys Platform Architect provides conversion modules between Synopsys SCML2 Fast Timed (FT) and ARM AMBA TLM 2.0 interfaces, enabling the NoC model to integrate with existing system models without custom glue logic.

This standards-based approach helps ensure flexibility across different system architectures and modeling environments.

The simulator also provides detailed visibility into NoC behavior.

Architects can analyze metrics such as:

Fig 1. NoC and traffic visibility

Such visibility helps architects understand where bandwidth constraints emerge, which routers experience congestion, and how workload patterns influence overall system performance.

FabricStudio simplifies the process of generating and integrating the NoC model.

Starting from a Python-based configuration, a single command will be able to generate:

As system complexity grows, the industry is increasingly shifting toward architecture-first design methodologies, where data movement, topology, and traffic behavior are explored before RTL implementation begins. Integrations such as the emerging FabricStudio–Platform Architect workflow aim to give architects a practical way to evaluate interconnect behavior early in the design cycle—reducing risk and helping teams move from architectural concept to silicon with greater confidence.