It is a question worth asking. In the rapidly evolving field of AI chip design, many teams pour significant resources into developing custom in-house fabrics to gain a system-level competitive advantage. While the goal of optimizing data movement is compelling, the results frequently fall short of expectations.

These internally developed fabrics frequently lack critical features, stumble on scalability, inflate engineering cost, and delay time to market. Worse, they consume precious engineering bandwidth, forcing system architects to battle infrastructure rather than build innovation.

And now, we’re witnessing a powerful industry shift. Design teams that previously built their own in-house fabrics are transitioning to Baya’s fabric platform – even midstream in active programs. Just in the past three months, two major teams made the switch. The results:

These are not teams that compromise; they have decades of fabric and system design experience. They’re choosing a better foundation, one that enables velocity, flexibility, and future-proof scaling.

Yes, we offer best-in-class technology. But customers are not switching to Baya just for better KPIs or better support. They’re choosing us because our solution fundamentally changes how fabric gets done.

What teams are gaining:

But beyond features, it’s our core philosophy and execution discipline that sets us apart.

From the beginning, we’ve focused on keeping our fabric architecture lean, scalable, and standards aligned. That has meant saying “no” to certain features and even walking away from short-term business – tough calls for any early-stage company.

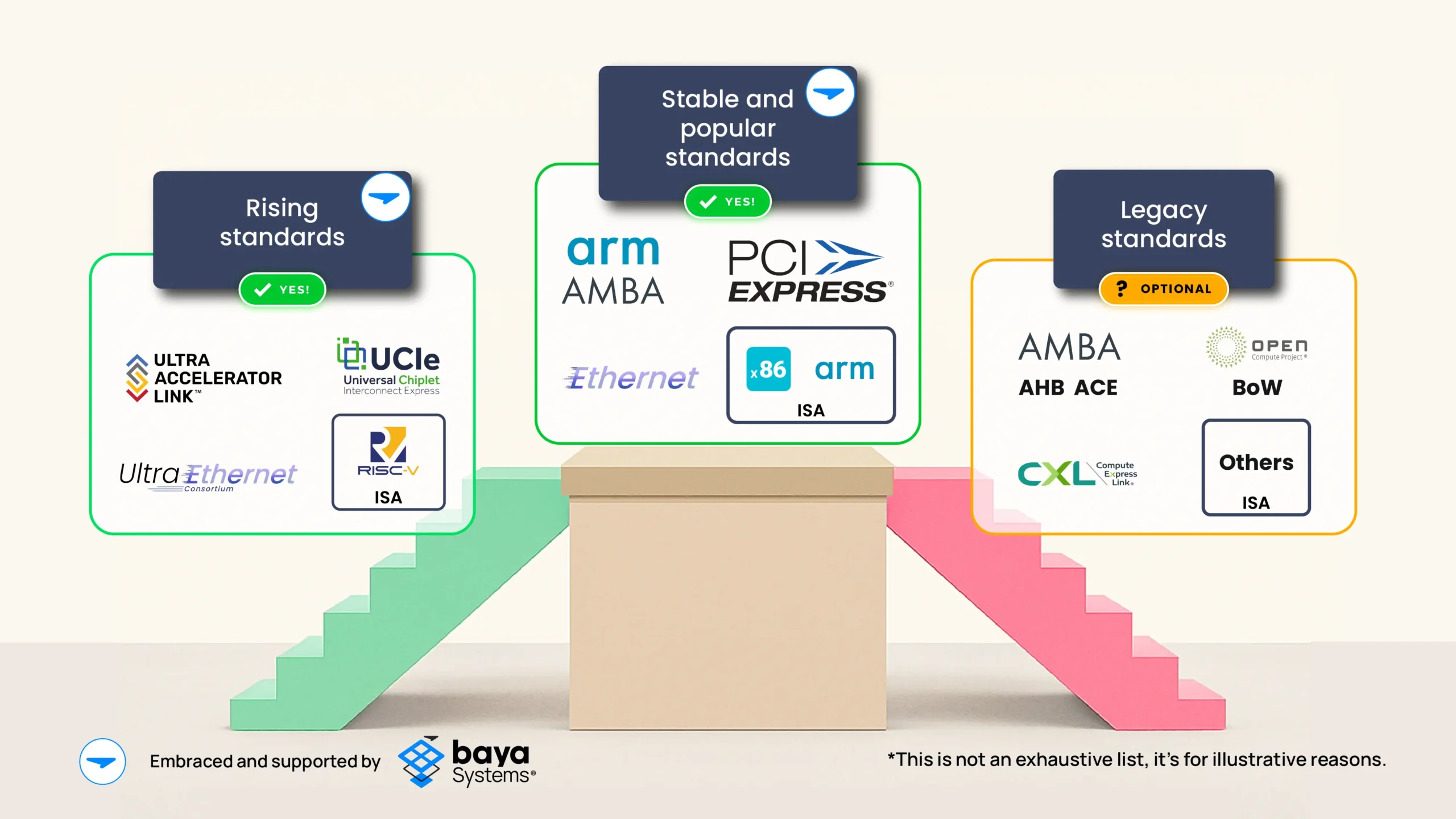

We chose to align with a curated set of winning standards, based on long-term scalability and industry momentum – not legacy compatibility. This is based on our intensive market research and feedback gathering. This decision has led to a clean, efficient architecture that consistently delivers better KPIs, easier integration, and faster design closure.

Like RISC vs CISC and IP vs ATM, history rewards simplicity and focus.

Here’s how we see the fabric and system standards landscape (If you disagree, please let us know, always happy to discuss more and support):

We also apply this mindset throughout

our architecture, roadmap and feature development. We avoid bloat, but when

customers need targeted extensions that add real value, we support it – selectively,

and with discipline. We deliver flexibility, customizability and extensibility

as optimally as possible.

Even the most seasoned design teams can fall into the trap of fighting against the natural constraints of silicon. At Baya, we take a different approach. We align every aspect of our design and architecture – from hardware to software – around the limits of physics and scaling trends. Here are a few common mistakes we often see, even among top-tier teams:

a. Trading off Gates for Wires

b. Ignoring Chiplet Bandwidth Realities

c. Mixing Compute and Switching Logic

d. Assuming Flat UMA Across Chiplets

The Bottom Line:

At Baya, we design every part of our platform – from physical architectures to software methodology – around these physical realities, ensuring our customers can scale with confidence as process nodes evolve and system complexity grows. By aligning our design choices with real-world silicon trends and physics, we make time our friend, not our enemy.

What truly sets Baya apart is not just the IP itself – it’s the end-to-end design methodology powered by a deeply invested, software-first platform.

Our entire approach is software-defined, anchored by a Python-based API and a highly extensible framework. This isn’t a bolt-on utility. It’s the core design and integration interface for our fabric IP, developed with a singular focus: to give engineers unparalleled speed, control, and insight throughout the development cycle.

We’ve made significant, multi-year investments into building this platform – not just as tooling, but as the foundation of our product. The result is a flow that allows customers to:

This platform supports everything from single-die SoCs to complex chiplet systems, with full support for hierarchical designs, observability, reprogrammability, and customizable configuration interfaces.

Customers repeatedly tell us:

“We’ve never seen fabric design and integration this programmable or this fast.”

And we’re confident in saying: no one else offers this level of extensibility and power – not legacy vendors, and not internal tools. Our system has been purpose-built to cover every phase: from architecture to RTL, to physical closure, to post-silicon tuning.

It doesn’t just help you design fabric faster – it changes what your team can deliver.

The technology matters – but so does the team behind it.

At Baya, we’ve built a team that earns the trust and respect of the best architects and silicon leads in the industry. We work shoulder to shoulder with engineering teams at some of the world’s top hyperscaler and semiconductor companies, helping them rethink how they build systems.

From evaluation to deployment to post-silicon tuning, our team stays deeply involved. We give honest guidance, push for clean design choices, and go above and beyond to make customers successful.

This close engagement model doesn’t scale easily – but it works. And we’ll scale it thoughtfully as we grow. If you’re a top-tier engineer who cares about fabrics, there’s no better place to be than Baya.

While much of our momentum has come from winning new design starts, we’re now seeing something new and even more significant: teams are beginning to transition existing projects midstream to adopt Baya’s fabric IP.

That’s a remarkable shift. In the world of semiconductors, teams are notoriously cautious about changing architectural components during development – especially critical ones like fabric. The risk and integration overhead usually outweigh the benefit. But not anymore.

Two major teams have made that leap in last quarter alone. These are not experimental projects – they are core product lines with high visibility and demanding schedules. Yet these teams concluded that their in-house fabrics had become a bottleneck: inflexible, costly, and hard to maintain.

With Baya, the transition has been smooth. Thanks to our modular architecture and robust software tooling, teams can rapidly validate new topologies, integrate RTL, and re-run key workflows – within weeks, not quarters.

What’s more, our team actively supports these transitions, providing:

This is a major vote of confidence – not just in our technology, but in the pragmatic, scalable way we deliver it.

So, if you’re mid-flight on a project and feel your fabric is holding you back – know that it’s not too late to switch.

We’ve helped others do it. And we can help you too.

The Bottom Line:

The chip industry has a long tradition of reinventing the wheel, but the game has changed. In the era of chiplet-scale systems, speed, modularity, and scalability are the real differentiators. Building every layer from scratch can feel like control, but it often just locks in inefficiency. The most innovative teams are now choosing to outsource complexity, focusing their talent where it matters. A clean, standards-driven fabric isn’t just a better technical choice — it’s a strategic one, and it’s what the fastest teams are choosing today.

If you’re still wrestling with legacy, in-house fabrics, it’s time to ask the tough question:

Is your fabric accelerating innovation – or slowing you down?

Either way, we’d love to talk. You might be surprised by what’s possible when the right architecture, methodology, and team come together.